探秘芯片世界剖析多层次设计之谜

在现代电子产品中,芯片是最核心的组成部分,它们不仅决定了设备的性能,还影响着能效和成本。然而,当我们提到芯片时,我们通常会被一个问题所困扰:芯片有几层?这似乎是一个简单的问题,但实际上背后涉及到的技术深度非常之大。

芯片的基本构造

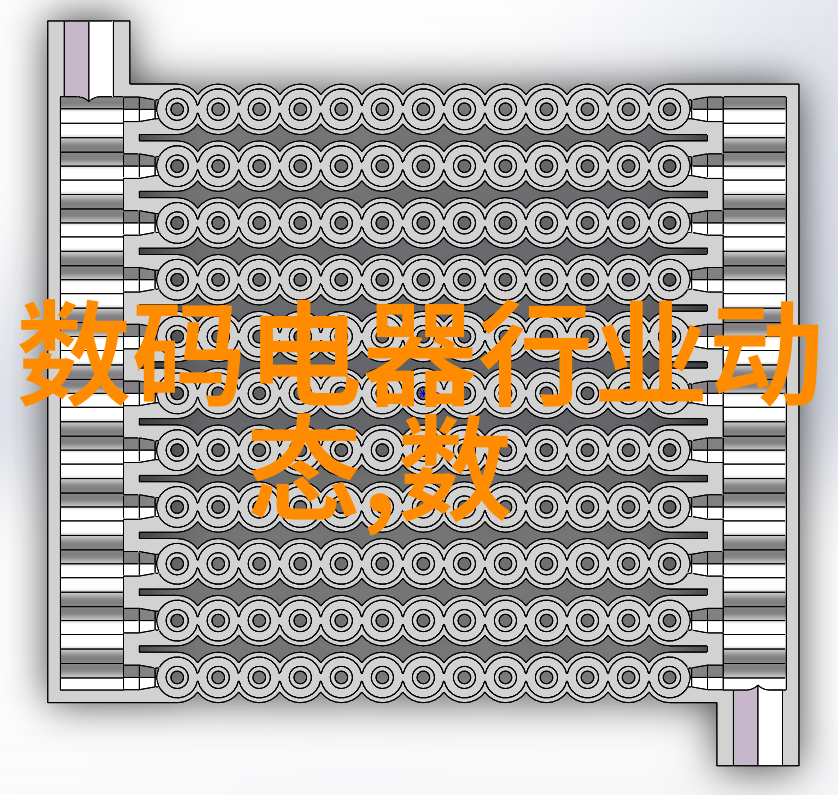

首先要了解的是,芯片本质上是一种集成电路,这意味着它将多个功能性元件(如晶体管、电阻等)集成在一个小型化的硅基板上。这些元件通过精密加工和微观结构来实现复杂的电子功能。在这个基础上,随着科技进步,一些更先进的制造工艺使得单一层面上的元件变得更加紧凑和复杂,从而形成了多层级别的结构。

多层次设计之初

当我们谈论“芯片有几层”时,其实是在询问其内部架构。当第一代集成电路出现时,由于技术限制,大概只有数十个门级别,即相当于两三层。但随着时间推移,尤其是1990年代以后,以半导体材料为主体进行的大规模集成技术,使得每一代新的处理器都比前一代具有更多元件,因此也逐渐增加了层数。

跨过摩尔定律

摩尔定律指出,每18个月计算能力就会翻倍,而面积却保持不变。这意味着为了维持同样的性能水平,每隔一段时间就需要减少物理尺寸,这样才能实现计算能力提升。这对于提高集成度至关重要,也直接关系到“芯chip 有几層”的答案。在这个过程中,不断创新和改进制造工艺,使得每一次缩小尺寸都伴随着新颖的手段,如使用更高纯度硅、引入新材料或改善光刻技术等。

传感器与MEMS应用

除了标准逻辑IC外,现在还有一类特殊类型叫做传感器与微机电系统(MEMS),它们专门用于检测环境变化,比如温度、压力、磁场或加速度。这些传感器可以独立作为单独的小型化设备存在,也可以嵌入到其他大的系统中以提供特定的信息。由于它们主要依赖于机械运动,所以需要额外考虑振动隔离以及适应不同工作条件下的稳定性,这也是为什么人们说“chip has many layers”。

新兴领域——3D栈与超薄堆叠

近年来,一些研究者开始尝试利用垂直堆叠技术来进一步扩展单个晶圆上的可用空间。这就是所谓的3D栈(Stacks)。通过将不同的部件按照一定规则并列或者交错地堆叠起来,可以有效地减少整个系统占用的空间,同时又保留了良好的信号通讯路径。此外还有超薄堆叠方法,比如采用低功耗处理器替换掉厚重且功耗较大的旧款CPU,并结合其他相关硬件优化整合,使得总体厚度降低但性能仍然得到提升。

未来的发展趋势分析

未来,对于如何进一步提高晶圆上的组装密度,以及如何解决热管理问题,将是关键挑战之一。而另一方面,由于全球能源消耗日益增长,对能效要求越发严格,因此研发高效能/低功耗(Energy-Efficient Low Power, EELP)的新型半导体材料及制程将成为重点方向。此外,在量子计算领域,也有可能出现全新的“layers”概念,因为量子比特对环境噪声极为敏感,与此同时也蕴含巨大的潜力值,只要能够克服当前面临的一系列难题的话,那么未来我们的讨论内容可能会完全改变过去关于"chip has many layers"的问题思考方式。